邏輯門展區II

邏輯門是數碼電子學中的基本組成部份。邏輯門輸入和輸出之間的關係可以用真值表來表示。

異或非門和異或門

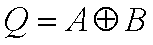

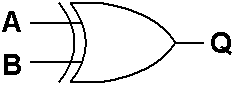

異或門是一種具有兩個或多個輸入的邏輯門,當輸入中只有一個為1時,邏輯門的輸出才為1。圖1是一個二輸入異或門的電路符號,而表1是它的真值表。

異或門所執行的邏輯運算可表示為:

圖1: 異或門的電路符號

| A | B | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

表1: 異或門的真值表

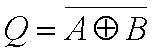

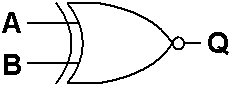

異或非門是一種具有兩個或多個輸入的邏輯門,只有當所有輸入都為同一邏輯狀態時,邏輯門的輸出才為1。圖2是一個二輸入異或非門的電路符號,而表2是它的真值表。

異或非門所執行的邏輯運算可表示為:

圖2: 異或非門的電路符號

| A | B | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

表2: 異或非門的真值表

半加器和基本 (1位元) 全加器

在電子學中,加法器是一種實現兩個數加法運算的設備。

半加器是一種實現1位元加法的邏輯電路。P和Q都是1位元二進制數。S是P和Q的1位元和而CO是進位輸出位元。圖3顯示數學上P和Q的2位元算術和,它由兩個輸出S和CO組成,其中CO是最高有效位元 (MSB)。圖4是1位元加法的所有可能情況,表3是半加器的真值表。

| 1 | ←P | ||

| +) | 1 | ←Q | |

| 1 | 0 | ||

| ↑ | ↑ | ||

| 進位 | 和 | ||

圖3: 兩個1位元二進數的加法運算

| 0 + 0 = 0 |

| 0 + 1 = 1 |

| 1 + 0 = 1 |

| 1 + 1 = 0 進位為1 |

圖4: 1位元加法的所有可能情況

| 輸入 | 輸出 | ||

|---|---|---|---|

| P | Q | CO | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

表3: 半加器的真值表

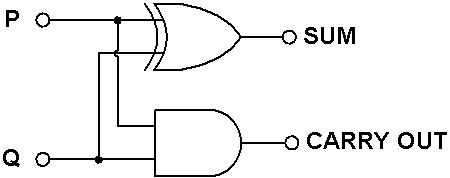

根據真值表的結果,若從邏輯運算上考慮半加器的輸入輸出關係,S是兩個輸入經過異或 (XOR) 運算的結果,而CO是兩個輸入經過與 (AND) 運算的結果。這表示半加器電路能夠只用兩種門電路實現:一個異或門和一個與門,見圖5。

圖5: 半加器

由於半加器不能接受來自低位相加所產生的進位位元作為輸入,因此它只能執行兩個1位元二進制數的加法。

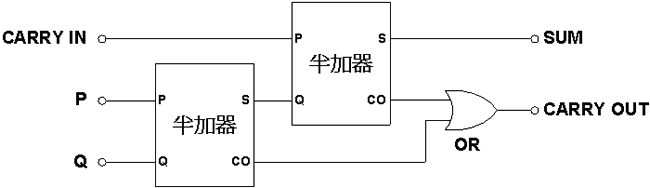

基本 (1位元) 全加器是實現兩個一位元二進數和一個進位輸入CARRY IN (CI) 加法運算的邏輯電路。它由一個或門和兩個半加器組成,見圖6。整個電路產生兩個輸出:S 和CO。多個全加器可以串接起來形成一個多位元加法器。

圖6: 基本 (1位元) 全加器

(4位元) 全加器

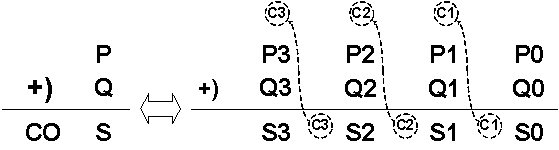

若干個基本 (1位元) 全加器可以串級成多位元全加器。如圖7所示,四個基本全加器被串級成一個4位元串行加法器,其中每個基本全加器的進位輸出CO接到下一有效位的全加器的進位輸入CI。

圖7: 由四個基本全加器構成的4位元串行加法器

兩個多位元二進制數P和Q的加法能夠由它們的最低有效位元 (LSB) 的相加開始,即P0 + Q0。任何前一位元的進位會相加到緊接的下一位元的和,見圖8。

圖8: 兩個4位元二進制數加法進位運算說明

對於一個5位元二進制數P,它的各個有效位元的數權值是:

| P0 = 20 = 1 |

| P1 = 21 = 2 |

| P2 = 22 = 4 |

| P3 = 23 = 8 |

| P4 = 24 = 16 |

把一個5位元二進制數P2 (P4 P3 P2 P1 P0) 轉換為相應的十進制數P10的公式是:

P10 = P4 x 24 + P3 x 23 + P2 x 22 + P1 x 21 + P0 x 20

一個4位元全加器的進位位元CO等同輸出的第4有效位元,而它的數權值為16 (24 = 16)。

由一個4位元全加器可得到的最大十進制和是31 (24+1 – 1 = 31)。

有關通訊博物館

聯絡

其他

其他網站

到訪人數:

最後更新日期: 10/3/2025