ТпМУХеЙЧјII

ТпМУХЪЧЪ§ТыЕчзгбЇжаЕФЛљБОзщГЩВПЗнЁЃТпМУХЪфШыКЭЪфГіжЎМфЕФЙиЯЕПЩвдгУецжЕБэРДБэЪОЁЃ

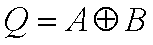

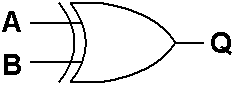

вьЛђЗЧУХКЭвьЛђУХ

вьЛђУХЪЧвЛжжОпгаСНИіЛђЖрИіЪфШыЕФТпМУХЃЌЕБЪфШыжажЛгавЛИіЮЊ1ЪБЃЌТпМУХЕФЪфГіВХЮЊ1ЁЃЭМ1ЪЧвЛИіЖўЪфШывьЛђУХЕФЕчТЗЗћКХЃЌЖјБэ1ЪЧЫќЕФецжЕБэЁЃ

вьЛђУХЫљжДааЕФТпМдЫЫуПЩБэЪОЮЊЃК

ЭМ1: вьЛђУХЕФЕчТЗЗћКХ

| A | B | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Бэ1: вьЛђУХЕФецжЕБэ

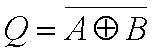

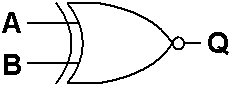

вьЛђЗЧУХЪЧвЛжжОпгаСНИіЛђЖрИіЪфШыЕФТпМУХЃЌжЛгаЕБЫљгаЪфШыЖМЮЊЭЌвЛТпМзДЬЌЪБЃЌТпМУХЕФЪфГіВХЮЊ1ЁЃЭМ2ЪЧвЛИіЖўЪфШывьЛђЗЧУХЕФЕчТЗЗћКХЃЌЖјБэ2ЪЧЫќЕФецжЕБэЁЃ

вьЛђЗЧУХЫљжДааЕФТпМдЫЫуПЩБэЪОЮЊЃК

ЭМ2: вьЛђЗЧУХЕФЕчТЗЗћКХ

| A | B | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Бэ2: вьЛђЗЧУХЕФецжЕБэ

АыМгЦїКЭЛљБО (1ЮЛдЊ) ШЋМгЦї

дкЕчзгбЇжаЃЌМгЗЈЦїЪЧвЛжжЪЕЯжСНИіЪ§МгЗЈдЫЫуЕФЩшБИЁЃ

АыМгЦїЪЧвЛжжЪЕЯж1ЮЛдЊМгЗЈЕФТпМЕчТЗЁЃPКЭQЖМЪЧ1ЮЛдЊЖўНјжЦЪ§ЁЃSЪЧPКЭQЕФ1ЮЛдЊКЭЖјCOЪЧНјЮЛЪфГіЮЛдЊЁЃЭМ3ЯдЪОЪ§бЇЩЯPКЭQЕФ2ЮЛдЊЫуЪѕКЭЃЌЫќгЩСНИіЪфГіSКЭCOзщГЩЃЌЦфжаCOЪЧзюИпгааЇЮЛдЊ (MSB)ЁЃЭМ4ЪЧ1ЮЛдЊМгЗЈЕФЫљгаПЩФмЧщПіЃЌБэ3ЪЧАыМгЦїЕФецжЕБэЁЃ

| 1 | ЁћP | ||

| +) | 1 | ЁћQ | |

| 1 | 0 | ||

| Ёќ | Ёќ | ||

| НјЮЛ | КЭ | ||

ЭМ3: СНИі1ЮЛдЊЖўНјЪ§ЕФМгЗЈдЫЫу

| 0 + 0 = 0 |

| 0 + 1 = 1 |

| 1 + 0 = 1 |

| 1 + 1 = 0 НјЮЛЮЊ1 |

ЭМ4: 1ЮЛдЊМгЗЈЕФЫљгаПЩФмЧщПі

| ЪфШы | ЪфГі | ||

|---|---|---|---|

| P | Q | CO | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Бэ3: АыМгЦїЕФецжЕБэ

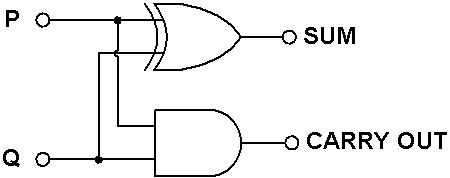

ИљОнецжЕБэЕФНсЙћЃЌШєДгТпМдЫЫуЩЯПМТЧАыМгЦїЕФЪфШыЪфГіЙиЯЕЃЌSЪЧСНИіЪфШыОЙ§вьЛђ (XOR) дЫЫуЕФНсЙћЃЌЖјCOЪЧСНИіЪфШыОЙ§гы (AND) дЫЫуЕФНсЙћЁЃетБэЪОАыМгЦїЕчТЗФмЙЛжЛгУСНжжУХЕчТЗЪЕЯжЃКвЛИівьЛђУХКЭвЛИігыУХЃЌМћЭМ5ЁЃ

ЭМ5: АыМгЦї

гЩгкАыМгЦїВЛФмНгЪмРДздЕЭЮЛЯрМгЫљВњЩњЕФНјЮЛЮЛдЊзїЮЊЪфШыЃЌвђДЫЫќжЛФмжДааСНИі1ЮЛдЊЖўНјжЦЪ§ЕФМгЗЈЁЃ

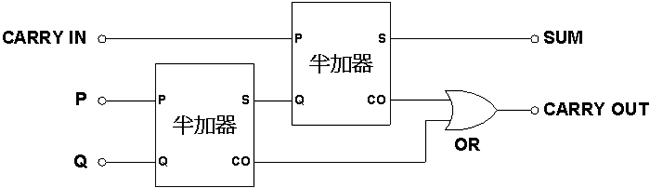

ЛљБО (1ЮЛдЊ) ШЋМгЦїЪЧЪЕЯжСНИівЛЮЛдЊЖўНјЪ§КЭвЛИіНјЮЛЪфШыCARRY IN (CI) МгЗЈдЫЫуЕФТпМЕчТЗЁЃЫќгЩвЛИіЛђУХКЭСНИіАыМгЦїзщГЩЃЌМћЭМ6ЁЃећИіЕчТЗВњЩњСНИіЪфГіЃКS КЭCOЁЃЖрИіШЋМгЦїПЩвдДЎНгЦ№РДаЮГЩвЛИіЖрЮЛдЊМгЗЈЦїЁЃ

ЭМ6: ЛљБО (1ЮЛдЊ) ШЋМгЦї

(4ЮЛдЊ) ШЋМгЦї

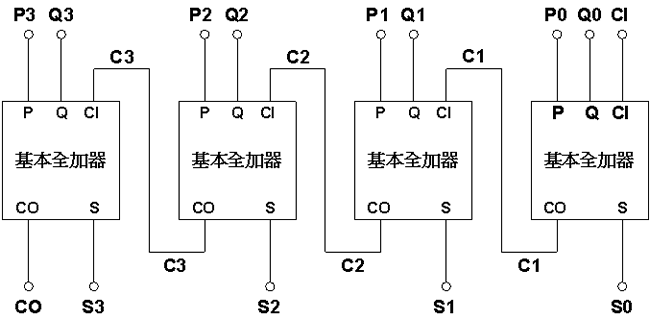

ШєИЩИіЛљБО (1ЮЛдЊ) ШЋМгЦїПЩвдДЎМЖГЩЖрЮЛдЊШЋМгЦїЁЃШчЭМ7ЫљЪОЃЌЫФИіЛљБОШЋМгЦїБЛДЎМЖГЩвЛИі4ЮЛдЊДЎааМгЗЈЦїЃЌЦфжаУПИіЛљБОШЋМгЦїЕФНјЮЛЪфГіCOНгЕНЯТвЛгааЇЮЛЕФШЋМгЦїЕФНјЮЛЪфШыCIЁЃ

ЭМ7: гЩЫФИіЛљБОШЋМгЦїЙЙГЩЕФ4ЮЛдЊДЎааМгЗЈЦї

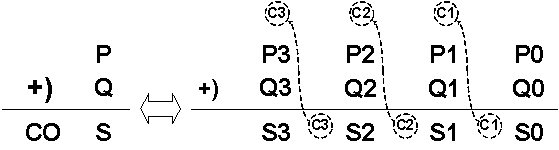

СНИіЖрЮЛдЊЖўНјжЦЪ§PКЭQЕФМгЗЈФмЙЛгЩЫќУЧЕФзюЕЭгааЇЮЛдЊ (LSB) ЕФЯрМгПЊЪМЃЌМДP0 + Q0ЁЃШЮКЮЧАвЛЮЛдЊЕФНјЮЛЛсЯрМгЕННєНгЕФЯТвЛЮЛдЊЕФКЭЃЌМћЭМ8ЁЃ

ЭМ8: СНИі4ЮЛдЊЖўНјжЦЪ§МгЗЈНјЮЛдЫЫуЫЕУї

ЖдгквЛИі5ЮЛдЊЖўНјжЦЪ§PЃЌЫќЕФИїИігааЇЮЛдЊЕФЪ§ШЈжЕЪЧЃК

| P0 = 20 = 1 |

| P1 = 21 = 2 |

| P2 = 22 = 4 |

| P3 = 23 = 8 |

| P4 = 24 = 16 |

АбвЛИі5ЮЛдЊЖўНјжЦЪ§P2 (P4 P3 P2 P1 P0) зЊЛЛЮЊЯргІЕФЪЎНјжЦЪ§P10ЕФЙЋЪНЪЧ:

P10 = P4 x 24 + P3 x 23 + P2 x 22 + P1 x 21 + P0 x 20

вЛИі4ЮЛдЊШЋМгЦїЕФНјЮЛЮЛдЊCOЕШЭЌЪфГіЕФЕк4гааЇЮЛдЊЃЌЖјЫќЕФЪ§ШЈжЕЮЊ16 (24 = 16)ЁЃ

гЩвЛИі4ЮЛдЊШЋМгЦїПЩЕУЕНЕФзюДѓЪЎНјжЦКЭЪЧ31 (24+1 ЈD 1 = 31)ЁЃ

гаЙиЭЈбЖВЉЮяЙн

СЊТч

ЦфЫћ

ЦфЫћЭјеО

ЕНЗУШЫЪ§ЃК

зюКѓИќаТШеЦкЃК 10/3/2025