ДЅЗЂЦїЕчТЗеЙЧј

гЩJ-K ДЅЗЂЦїзщГЩЕФЖўНјжЦМЦЪ§Цї

D ДЅЗЂЦї

ЫјДцЦїЪЧвЛжжЛљБОЕФМЧвфЦїМўЃЌЫќФмЙЛДЂДцвЛЮЛдЊЕФЪ§ОнЁЃгЩгкЫќЪЧвЛжжЪБађадЕФЕчТЗЃЌЫљвдВЂВЛашвЊЪБжгЪфШыЃЌЫќЛсИљОнЪфШыРДИФБфЪфГіЁЃ

ДЅЗЂЦїВЛЭЌгкЫјДцЦїЃЌЫќЪЧвЛжжЪБжгПижЦЕФМЧвфЦїМўЃЌДЅЗЂЦїОпгавЛИіПижЦЪфШыбЖКХ (CLOCK)ЁЃCLOCKбЖКХЪЙДЅЗЂЦїжЛдкЬиЖЈЪБПЬВХАДЪфШыбЖКХИФБфЪфГізДЬЌЁЃШєДЅЗЂЦїжЛдкЪБжгCLOCKгЩLЕНH (HЕНL) ЕФзЊЛЛЪБПЬВХНгЪеЪфШыЃЌдђГЦетжжДЅЗЂЦїЪЧЩЯЩ§би (ЯТНЕби) ДЅЗЂЕФЁЃ

ДЅЗЂЦїПЩгУРДДЂДцвЛЮЛЕФЪ§ОнЁЃЭЈЙ§НЋШєИЩИіДЅЗЂЦїСЌНгдквЛЦ№ПЩДЂДцЖрЮЛдЊЕФЪ§ОнЃЌЫќУЧПЩгУРДБэЪОЪБађЦїЕФзДЬЌЁЂМЦЪ§ЦїЕФжЕЁЂЕчФдМЧвфЬхжаЕФASCIIТыЛђЦфЫћзЪСЯЁЃ

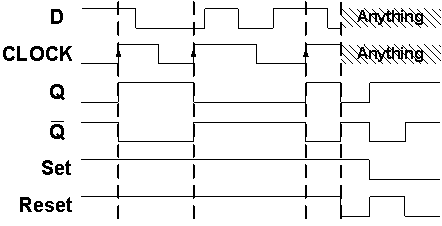

DДЅЗЂЦїЪЧзюГЃгУЕФДЅЗЂЦїжЎвЛЁЃЖдгкЩЯЩ§биДЅЗЂDДЅЗЂЦїРДЫЕЃЌЦфЪфГіQжЛдкCLOCKгЩLЕНHЕФзЊЛЛЪБПЬВХЛсИњЫцЪфШыDЕФзДЬЌЖјБфЛЏЃЌЦфЫћЪБКђQдђЮЌГжВЛБфЁЃЭМ1ЯдЪОСЫЩЯЩ§биДЅЗЂDДЅЗЂЦїЕФЪБађЭМЃЌБэ1дђЪЧЦфецжЕБэЁЃ

ЭМ 1: ЩЯЩ§биДЅЗЂDДЅЗЂЦїЕФЪБађЭМ

Бэ 1: DДЅЗЂЦїЕФецжЕБэ

SETКЭRESETЪЧDДЅЗЂЦїжаЖюЭтСНИіПЩвдЦСБЮЪБжгВйзїЕФЪфШыЁЃDДЅЗЂЦїе§ГЃЙЄзїЧщПіЯТЃЌSETКЭRESETОљБиаыЩшЮЊ1ЁЃ

зюдчЕФЕчзгДЅЗЂЦїгк1919ФъЗЂУїЁЃЯжНёдкЪБађПижЦЯЕЭГжаЃЌзюГЃгУЕФЫФжжДЅЗЂЦїЗжБ№ЮЊЃКTаЭДЅЗЂЦїЁЂS-RДЅЗЂЦїЁЂJ-KДЅЗЂЦїМАDДЅЗЂЦїЁЃ

гЩJ-K ДЅЗЂЦїзщГЩЕФЖўНјжЦМЦЪ§Цї

МЦЪ§ЦїЪЧвЛжжПЩДЂДцЛђЯдЪОЬиЖЈЪТМўЗЂЩњДЮЪ§ЕФЦїМўЃЌЭЈГЃгыЪБжгбЖКХгаЙиЁЃдкЕчзгбЇжаЃЌМЦЪ§ЦїПЩРћгУМђЕЅЕФМЧвфЦїМўРДжЦзїЃЌШчДЅЗЂЦїЕШЁЃ

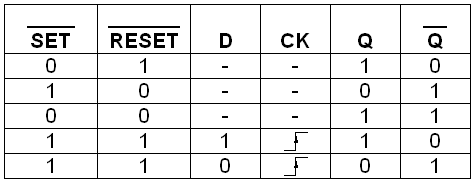

J-KДЅЗЂЦїЪЧзюГЃгУЕФДЅЗЂЦїжЎвЛЁЃБэ2ЪЧЯТНЕбиДЅЗЂJ-KДЅЗЂЦїЕФецжЕБэЁЃ

Бэ 2: J-K ДЅЗЂЦїЕФецжЕБэ

дкЭМ2жаЃЌЫФИіЯТНЕбиДЅЗЂJ-KДЅЗЂЦївдДЎНгФЃЪНСЌНгдквЛЦ№ЃЌЙЙГЩвЛИіЖўНјжЦМЦЪ§ЦїЁЃЦфжаУПИіДЅЗЂЦїЕФЪфГіQЖМБЛСЌНгЕНЯТвЛИіДЅЗЂЦїЕФЪБжгЪфШыCLOCKЃЌИљОнецжЕБэНЋУПИіДЅЗЂЦїЕФЪфШыJКЭKОљЩшЖЈЮЊ1ЃЌвђДЫДЅЗЂЦїдкЪБжгCLOCKУПДЮгЩHЕНLЕФзЊЛЛЪБПЬЖМЛсИФБфЦфзДЬЌЁЃ

ЭМ 2: J-K ДЅЗЂЦїЫљзщГЩЕФМЦЪ§ЦїЕФЪБађЭМ

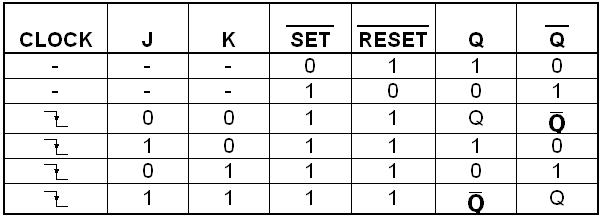

дкетИіЖўНјжЦМЦЪ§ЦїжаЃЌЫФИіЪфГіAжСDБэЪОвЛИі4ЮЛдЊЖўНјжЦЪ§ЃЌЦфжаAЪЧзюЕЭгааЇЮЛдЊ (LSB) ЖјDЪЧзюИпгааЇЮЛдЊ (MSB)ЁЃ

етИі4ЮЛдЊЖўНјжЦЪ§ЫцжјУПИіЪБжгCLOCKжмЦкЕФЕНРДЖјЕнді1ЁЃМЦЪ§ЦїгЩ (0)10 Ъ§жС (15)10ЃЌгждйЗЕЛи (0)10 ВЂвЛжБбЛЗЯТШЅЃЌМћБэ3ЁЃ

| ЪЎНјжЦ | ЖўНјжЦ | |||

|---|---|---|---|---|

| D | C | B | A | |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 |

| 10 | 1 | 0 | 1 | 0 |

| 11 | 1 | 0 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 |

| 14 | 1 | 1 | 1 | 0 |

| 15 | 1 | 1 | 1 | 1 |

Бэ3: 4ЮЛдЊЖўНјжЦМЦЪ§ЦїЕФецжЕБэ

8 ЮЛдЊвЦЮЛМФДцЦї

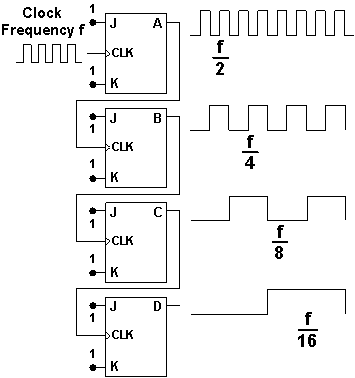

дкЪ§ТыЕчТЗжаЃЌМФДцЦїБЛгУзїДЂДцЪ§ОнгУЃЌМФДцЦїЭЈГЃгЩСНИіЛђСНИівдЩЯОпгаЙВЭЌЪБжг (CLOCK) ЪфШыЕФДЅЗЂЦїЫљзщГЩЁЃдкЕчФджаЃЌМФДцЦїГЃгУзїДЂДцвЛСЌДЎЕФЮЛдЊ (ЛђГЦЮЛдЊзщ) ЕФЪ§ОнЁЃ

вЦЮЛМФДцЦїЪЧвЛжжЖрЮЛдЊЕФМФДцЦїЃЌдкУПвЛИіCLOCKЕФзЊЛЛЪБПЬЃЌМФДцЦїжаЕФЪ§ОнНјаавЛЮЛдЊЕФвЦЮЛЁЃвЦЮЛМФДцЦїжавЛзщДЅЗЂЦївдДЎНгЕФаЮЪНЯрСЌЃЌМДУПИіДЅЗЂЦїЕФЪфГіЖМСЌНгЕНЯТвЛИіДЅЗЂЦїЕФЪфШыЁЃвђДЫЃЌУПДЮЪБжгЪфШыБЛДЅЗЂЪБЃЌЪ§ОнЛсж№вЛвЦЯђЯТвЛИіДЅЗЂЦїЁЃ

ЖдвЛИі8ЮЛдЊвЦЮЛМФДцЦїРДЫЕЃЌдкУПИіCLOCKгЩLжСHЕФзЊЛЛЪБПЬЃЌвЦЮЛМФДцЦїЖСШЁЪфШыDATAВЂАбЫќДЋЫЭжСЪфГіA0ЁЃA0жСA6ИїИіЮЛдЊЕФдгаЪ§жЕНЋвЦжСЯТвЛЮЛдЊ (МДA0вЦжСA1ЃЌA1вЦжСA2ЃЌЁЁЃЌA6вЦжСA7)ЃЌЖјA7ЕФЪ§жЕНЋБЛвЦГіМФДцЦїЃЌБэ1ЫЕУїСЫМФДцЦїЕФдЫзїЙ§ГЬЁЃ

| A0 | A1 | A2 | A3 | A4 | A5 | A6 | A7 | |

|---|---|---|---|---|---|---|---|---|

| ГѕЪМзДЬЌ | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ЪБжгжмЦк 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ЪБжгжмЦк 2 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| ЪБжгжмЦк 3 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| ЪБжгжмЦк 4 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| ЪБжгжмЦк 5 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| ЪБжгжмЦк 6 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| ЪБжгжмЦк 7 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| ЪБжгжмЦк 8 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Бэ 4: дк8ИіЪБжгжмЦкжаЃЌвЦЮЛМФДцЦїЕФвЦЮЛЙ§ГЬ

вЦЮЛМФДцЦїЕФЪфШыКЭЪфГіПЩвдЪЧДЎааЛђВЂааФЃЪНЁЃДЎааЪфШыЕФвтЫМЪЧЩшБИж№вЛЮЛдЊЖСШыЪ§ОнЃЌЖјВЂааЪфГіЕФвтЫМЪЧЫљгаЮЛдЊЭЌвЛЪБМфзїЮЊЪфГіЁЃР§ШчЃЌвЛИіДЎааЪфШыЁЂВЂааЪфГіЕФвЦЮЛМФДцЦїж№вЛЮЛдЊЖСШыЪ§ОнЃЌЖјЫљгаЪфГіЮЛдЊЭЌвЛЪБМфБЛЪфГіЁЃ

ДѓВПЗнЕчТЗвдЖрИіЮЛдЊЕФВЂааФЃЪНЙЄзїЃЌЖјДЎааНгПкдђОпгаНсЙЙМђЕЅЕФгХЕуЃЌЫљвдашвЊгавЛжжЩшБИЉЄЉЄвЦЮЛМФДцЦїРДЭъГЩДЎааНгПкКЭВЂааНгПкжЎМфЕФзЊЛЛЁЃ

вЦЮЛМФДцЦїПЩзїЮЊМђЕЅЕФбгЪБЕчТЗЁЃдкВЛЭЌЕФЪфГіЖЫ (A0жСA7) ПЩвдЕУЕНдкВЛЭЌЪБжгжмЦкбгЪБЯТЕФDATAбЖКХЁЃ

гаЙиЭЈбЖВЉЮяЙн

СЊТч

ЦфЫћ

ЦфЫћЭјеО

ЕНЗУШЫЪ§ЃК

зюКѓИќаТШеЦкЃК 10/3/2025